인더뉴스 이진솔 기자ㅣ 삼성전자가 GAA 기술로 파운드리 경쟁력을 높이고 있다. 이 분야에서는 라이벌 TSMC를 12개월 앞섰다는 평가가 나올 정도로 독주하고 있다.

삼성전자가 지난 14일(현지시간) 미국 산타클라라 메리어트 호텔에서 열린 ‘삼성 파운드리 포럼 2019’에서 3나노 공정 설계 키트를 제공했다. 삼성전자는 지난해 포럼에서 3나노 파운드리 공정 개발을 발표한 데 이어 3나노 미세공정 개발에 가까지워지고 있다.

미세공정의 성패는 트랜지스터 소형화에 달렸다. 전류를 흐르게 하거나 막아 칩이 데이터를 처리하는 방식을 제어하는 트랜지스터의 구조가 반도체의 성능과 전력효율에 영향을 미치기 때문이다.

또한 한 웨이퍼 위에서 가능한 많은 반도체 칩을 생산하려면, 트랜지스터 크기도 작아져야 한다. 웨이퍼 원판 트랜지스터 게이트 두께에 따라 공정의 미세한 정도가 달라진다.

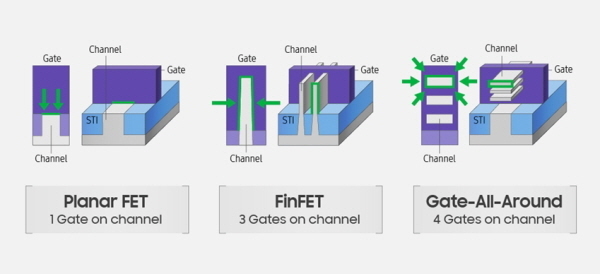

반도체에서 트랜지스터는 게이트가 소스(Source)와 드레인(Drain) 사이를 오가는 전류를 조절하는 역할을 한다. 기존 평면(Planar) 구조에서 게이트는 채널 상단에 고정됐다. 게이트와 채널의 접점이 클수록 반도체의 효율이 높아진다.

이어 도입된 핀펫(FinFET)은 3D 구조로 채널과 접촉면을 늘렸다. 평면 구조에서 접촉면이 한 면이었다면 핀펫 구조에서는 접촉면이 세 면으로 늘어난다. 보다 많은 접촉면에서 전력을 조절할 수 있어 전력 누설을 최소화했다.

이보다 발전된 GAA(Gate-All-Around) 구조는 채널을 원통형 나노와이어(Nanowire)로 만들어 게이트가 채널의 둘레를 모두 감싸고 있는 형태다. 다만 채널의 폭이 얇아 충분한 전류를 흐르게 하지 못하는 단점이 있다.

삼성전자가 독자 개발한 MBCFET™(Multi Bridge Channel FET)은 채널의 형태를 나노시트(Nanosheet)로 만들어 게이트에 닿는 채널 면적을 넓히는 기술이다. 게이트가 채널을 감싸는 구조는 GAA와 같지만 채널을 넓적한 형태로 바꿔 전류량을 증가시켰다.

삼성전자에 따르면 MBCFET™ 공정은 7나노 핀펫보다 칩 면적을 45%가량 줄일 수 있다. 웨이퍼에서 생산되는 칩 수가 두 배 가까이 늘어난다. 이어 소비전력은 약 50% 줄어들고 성능은 35% 향상될 것으로 기대된다.

삼성전자는 3나노 공정 개발 시기를 2020년으로 예상한다. 업계 관계자는 “개발 이후 양산까지 걸리는 시간을 고려하면 3나노 공정 양산은 2021년에 이뤄질 것”이라고 말했다.

공정 미세화에 박차를 가하면서 경쟁사인 대만 TSMC와 미국 인텔을 기술력에서 앞질렀다는 평가도 나온다. 컨설팅 회사 IBS의 헨델 존스 CEO는 “삼성이 GAA기술에서 TSMC를 약 12개월 정도 앞섰다”며 “인텔은 2~3년 정도 뒤처져 있을 것”이라고 IT매체 씨넷(Cnet)을 통해 말했다.

![[인더필드] 더미식 신제품 ‘사천자장면’…하림은 확실한 2위 노린다](https://www.inthenews.co.kr/data/cache/public/photos/20240416/art_17134232137832_86acb8_120x90.jpg)