인더뉴스 권지영 기자ㅣ정부가 일본 수출규제 등 글로벌 소재전략무기화에 대응해 중·장기적 관점의 소재·부품·장비 기초·원천 연구개발(R&D) 예산을 대폭 확대한다.

과학기술정보통신부는 9일 올해 이 분야 기초·원천 R&D에 1600억 원을 투자한 데 이어 내년에는 3000억원을 투입한다고 밝혔다. 소재 분야 원천 기술을 확보하기 위해 ‘나노·미래소재 원천기술 개발사업’을 시작한다. 내년부터 2032년까지 진행되는 이 사업은 총 4004억 원이 지원된다.

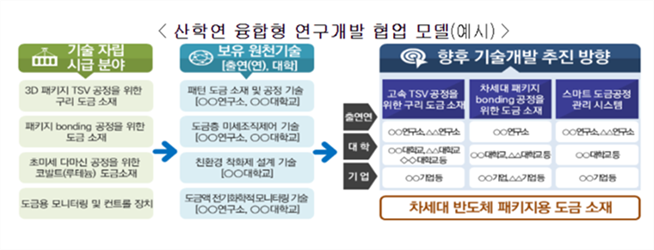

정부는 소재분야 기초연구 지원을 지속적으로 확대하고 있다. 특히 2020년에는 소재·부품 등에 특화된 기초연구실 60여개를 지정해 기초연구를 지원하고 대학과 정부 출연연구기관이 보유한 기술의 사업화를 지원하는 ‘소재혁신 선도 프로젝트’(가칭)에 326억원을 투자키로 했다.

방사광 가속기 기반의 반도체 검사용 극자외선(EUV) 광원 및 검사장비 개발에 내년 115억원을, 연구장비 국산화에는 73억원을 투입할 예정이다.

소재·부품 연구개발 주체 간 정보 개방과 공유 활성화를 위한 투자도 강화된다. 연구자들이 축적한 연구데이터를 함께 활용할 수 있게 데이터 플랫폼을 구축하는 데 2020~2025년 총 450억원을, 반도체 공공 테스트베드를 구축하는 데 올해부터 2022년까지 450억원을 각각 지원한다. 시스템 반도체 설계 중소기업(팹리스) 대상 성능검증 공정 지원에 올해부터 2022년까지 450억원을 투입한다.

아울러 과기정통부는 기초·원천 R&D 투자 효율을 높이기 위해 지금껏 11개 공공연구기관 중심으로 운영해 온 소재 연구기관 협의회를 확대 개편해 내년 ‘소재혁신전략본부’(가칭)를 출범시키기로 했다.

또 기술 수준과 산업 성숙도 등에 따라 R&D 지원방식도 차별화하기로 했다. 산업 경쟁력에 비해 기술 수준이 낮은 분야는 경쟁형 연구개발 방식을 통해 기술 수준의 조기 향상을 도모하고 기술 수준과 산업경쟁력이 모두 낮다면 연구자의 창의성이 극대화되도록 도전형 연구개발 방식을 도입하는 식이다.

과기정통부는 소재·부품·장비 기초·원천 R&D 사업에 대한 설명회를 매주 여는 한편 연구관리 전문기관의 소재·부품·장비 분야 연구관리 전문인력을 30여 명에서 50명 이상으로 확대할 예정이다.

한편, 문미옥 1차관은 이날 대전 SK이노베이션 기술혁신연구원을 찾아 대학, 출연연, 기업 관계자 등과 만나 소재·부품·장비 분야 기초원천 R&D 추진현황을 공유했다.

반도체 소재·부품 연구자와 중소기업 등이 실제 반도체 공정과 유사한 환경에서 연구결과와 시제품을 실증할 수 있도록 반도체 공공 테스트베드 구축(2019~2022년, 450억원)을 지원한다.