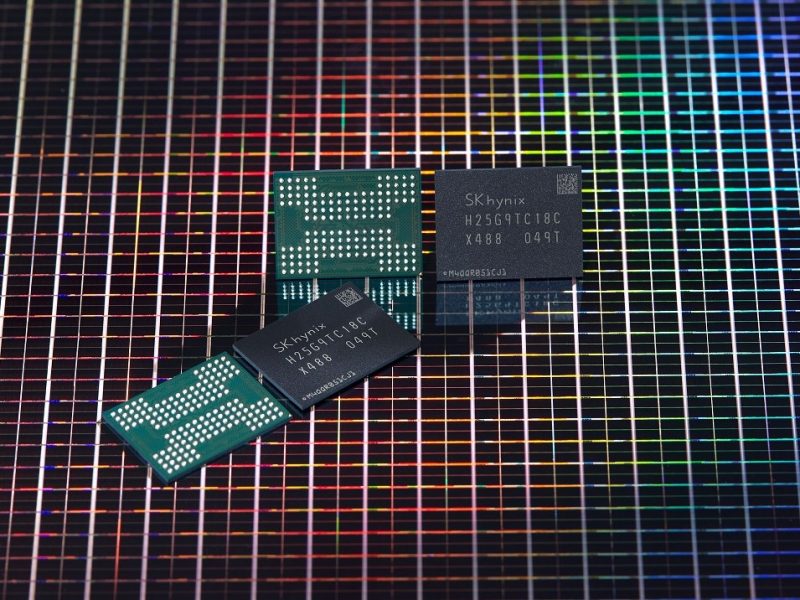

인더뉴스 권지영 기자ㅣSK하이닉스(대표이사 이석희)가 업계 최고층인 176단 512Gb(기가비트) TLC(Triple Level Cell) 4D 낸드플래시를 개발했다고 7일 밝혔습니다. SK하이닉스는 이 제품을 솔루션화하기 위해 지난달 컨트롤러 업체에 샘플을 제공했습니다.

SK하이닉스는 96단 낸드플래시부터 CTF(Charge Trap Flash)와 고집적 PUC(Peri Under Cell) 기술을 결합한 4D 제품을 시장에 선보이고 있습니다.

이번에 개발한 176단 낸드는 3세대 4D 제품으로 업계 최고 수준의 웨이퍼 당 생산 칩 수를 확보했는데요. 이를 통해 비트 생산성은 이전 세대보다 35% 이상 향상돼 차별화된 원가경쟁력을 갖출 수 있게 됐습니다.

2분할 셀 영역 선택 기술을 새롭게 적용해 셀(Cell)에서의 읽기 속도는 이전 세대 보다 20% 빨라졌습니다. 또한 공정 수 증가 없이 속도를 높일 수 있는 기술도 적용해 데이터 전송 속도는 33% 개선된 1.6Gbps를 구현했습니다.

SK하이닉스는 내년 중반, 최대 읽기 속도 약 70%, 최대 쓰기 속도 약 35%가 향상된 모바일 솔루션 제품을 시작으로 소비자용 SSD와 기업용 SSD를 순차적으로 출시하는 등 응용처별 시장을 확대해 나갈 예정입니다.

낸드플래시는 층수가 높아지면서 셀 내부의 전류 감소, 층간 비틀림 및 상하 적층 정렬 불량(Stack misalignment)에 따른 셀 분포 열화 현상 등이 발생하게 됩니다.

SK하이닉스는 이러한 어려움을 ▲ 셀 층간 높이 감소 기술 ▲ 층별 변동 타이밍(Timing) 제어 기술 ▲ 초정밀 정렬(alignment) 보정 등 혁신적인 기술로 극복하고 업계 최고 수준의 176단 낸드를 개발했습니다.

또한 176단 4D 낸드 기반으로 용량을 2배 높인 1Tb(테라비트) 제품을 연속적으로 개발해 낸드플래시 사업 경쟁력을 높여 나간다는 방침입니다.

최정달 SK하이닉스 낸드개발 담당은 “낸드플래시 업계는 집적도 향상과 생산성 극대화를 동시에 달성하기 위해 기술 개발에 매진하고 있다”며 “SK하이닉스는 4D 낸드의 개척자로서 업계 최고의 생산성과 기술력으로 낸드플래시 시장을 선도해 나갈 것”이라고 말했습니다.

한편, 시장조사기관 옴디아는 2020년 4318억GB인 낸드플래시 시장이 2024년에는 1만 3662억GB로 확대돼 연평균 33.4% 성장할 것으로 예상하고 있습니다.

☞ 용어설명

4D 낸드- SK하이닉스는 2018년 96단 낸드플래시부터 CTF 셀 구조와 PUC 기술을 결합해 성능과 생산성을 동시에 구현한 차별성을 강조하기 위해 ‘4D 낸드플래시’로 명명.

CTF (Charged Trap Flash)- 전하를 도체(①)에 저장하는 플로팅 게이트(Floating Gate)와 달리 전하를 부도체(②)에 저장해 셀간 간섭 문제를 해결한 기술로, 플로팅게이트 기술보다 단위당 셀 면적을 줄이면서도 읽기, 쓰기 성능을 높일 수 있는 것이 특징. 대부분의 3D 낸드 업체는 CTF를 채용 중임.

PUC(Peri Under Cell)- 주변부(Peri.) 회로를 셀 회로 하단부에 배치해 생산효율을 극대화하는 기술.

2분할 셀 영역 선택 기술- 낸드플래시 회로에서 워드라인(Word Line)은 셀(Cell)에 전압을 인가하는 역할을 하고 있음. 적층수가 높아질수록 셀의 층고를 낮추기 위해 워드라인도 얇게 구현하는데, 이때 워드라인에 인가되는 저항이 커지면 속도에 영향을 받게 됨. 워드라인에 연결된 셀을 기존 대비 절반으로 분할해 저항을 낮춤에 따라 전압인가 시간을 단축하고 읽기 동작 속도를 향상시킴.

셀(Cell) 층간 높이 감소 기술- 적층 수가 높아지면 셀 형성을 위한 구멍을 뚫기 어려워지고, 저항 증가 및 전류 감소로 성능과 신뢰성을 확보하기 어려워 짐. 이를 해결하기 위해서는 층간 높이를 최대한 낮추는 것이 필요하나 이 경우, 셀간 간섭이 심해지고 공정 불량이 발생할 가능성이 높아짐. 셀 층간 높이 감소 기술은 층간 높이를 낮추면서도 성능/신뢰성의 열화를 억제하는 공정과 설계 기술로 176단의 층간 높이를 획기적으로 낮추면서도 경쟁력 있는 성능·신뢰성을 확보함.

층별 변동 타이밍 제어- 적층 수는 높이고 층고를 낮추다 보면 층간 비틀림 현상 증가와 더불어 셀 산포 열화가 많아짐. 이러한 공정 열화로 각 층별 성능과 신뢰성이 저하되는 현상이 발생함. 이를 해결하기 위해 각 층별 특성에 따라 가하는 전압의 양과 시간을 조절해 셀 특성을 균일하게 유지하고 성능과 신뢰성을 높이는 기술.

초정밀 정렬(alignment) 보정 기술- 업계는 적층 수가 높아짐에 따라 셀 형성을 위한 구멍을 한번에 뚫을 수가 없어 두 번에 걸쳐 뚫는 더블 스택(Double Stack) 공정을 활용하고 있음. 이때 상하부 간 어긋남을 최소화하는 것이 더블 스택 기술의 핵심임. 상하부가 바르게 정렬되지 않으면 상하부 간 전류 흐름이 원활하지 않게 되며 열화 현상도 발생해 수율과 성능·신뢰성이 감소하게 됨.

SK하이닉스는 2017년 72단 제품부터 적용해온 더블 스택 기술을 이번 176단 제품에도 적용했으며 그간의 노하우를 기반으로 공정 상 정렬 불일치(misalignment)를 실시간으로 파악하고 구멍의 위치와 크기를 자동으로 보정해주는 기술을 고도화 함.