인더뉴스 제해영 기자ㅣ국내 반도체 설계 전문 기업인 (주)태성환경연구소 나노팹기술개발센터(총괄책임자 임채록 이사, 수석연구원 정혁제 실장)는 고집적 D램(DRAM) 셀 설계 분야에서 차세대 기술 4건을 국내 특허로 등록했다고 27일 밝혔습니다.

이번 특허들은 기존 평면형 DRAM의 미세화 한계를 극복하고, 새로운 3차원 셀 구조 기반으로 집적도를 비약적으로 높일 수 있는 설계 기술을 담고 있습니다.

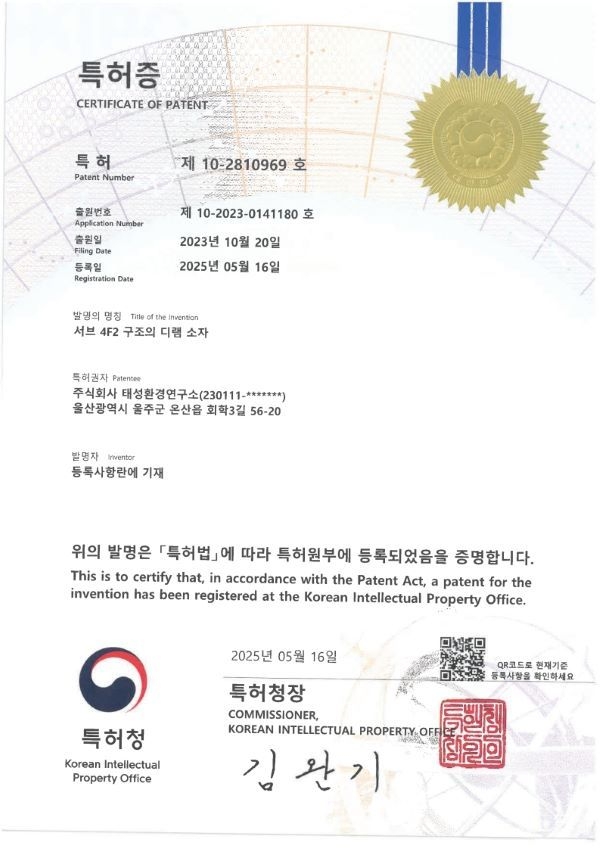

등록된 특허 중 첫 번째는 ’서브 4F2 구조의 디램 소자’로, 4F2 구조처럼 수직 방향의 셀 트랜지스터(이하 Tr.) 구조를 통해 전하 저장용 커패시터와 선택 Tr.을 구조상 단일 실리콘 기둥 내에 통합 구현한 것이 특징입니다.

더 나아가서 셀 면적을 3.5F2까지 줄일 수 있는데, 이는 기존 4F2 구조의 한계를 뛰어넘는 혁신적인 기술로, 워드 라인 이층 구조와 벌집 모양의 필라 배치를 통해 구현되었습니다. 이를 통해 셀 면적을 최소화하면서도 제조 공정의 정밀성과 수율을 동시에 확보할 수 있다고 설명했습니다.

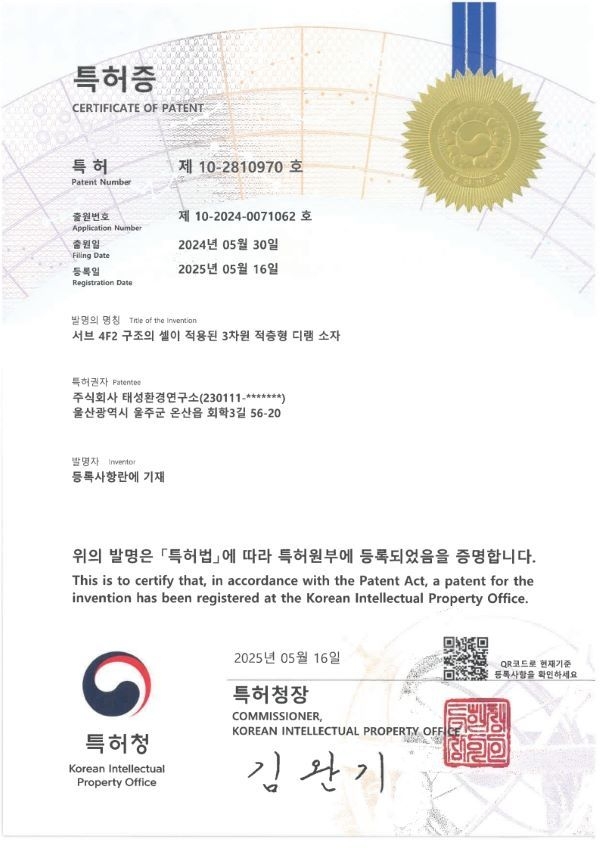

두 번째 특허는 ‘서브 4F2 구조의 셀이 적용된 3차원 적층형 디램 소자’인데요. 3.5F2 DRAM 셀을 3차원 적층형 D램에 적용함으로써 3차원 적층형 D램의 용량을 보다 증가시킬 수 있음을 입증했습니다. 이는 고용량 메모리 솔루션에 대한 시장의 요구를 충족시키는 데 핵심적인 역할을 할 전망입니다.

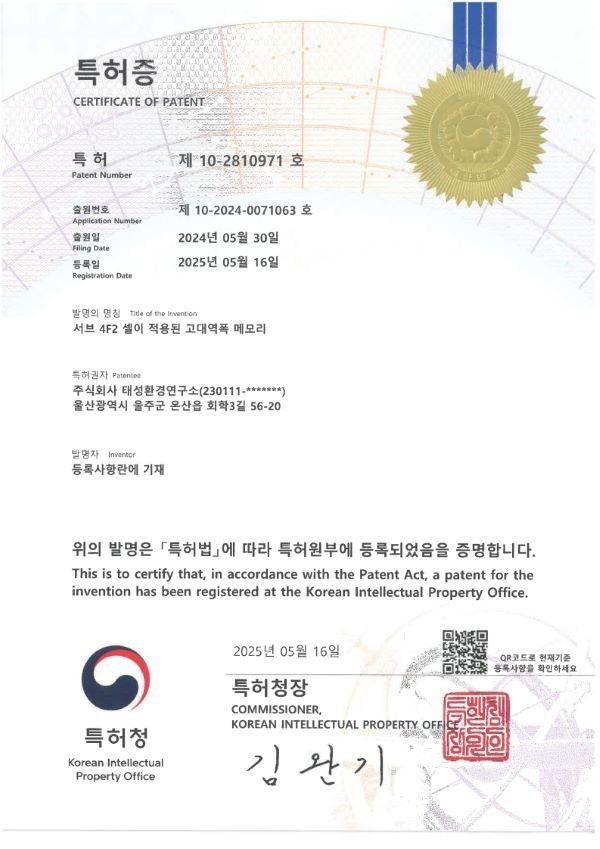

세 번째는 ‘서브 4F2 셀이 적용된 고대역폭 메모리’로, 3.5F2 D램 셀을 HBM에 적용하여 HBM의 용량을 대폭 증대시킬 수 있음과 HBM의 전력 효율을 높이는 데 크게 기여할 수 있음을 보여줍니다.

HBM은 데이터 처리량이 중요한 AI, 빅데이터 분석 등의 분야에서 필수적인 메모리로, 이 기술은 이러한 고성능 애플리케이션의 발전을 가속화할 것입니다. 또한 이 기술은 고온에서도 안정적인 동작 특성을 제공해 차세대 고속 서버 및 AI용 메모리에 적합하다는 평가를 받고 있습니다.

네 번째 특허는 ‘다층 워드라인 및 스위칭 절연막을 포함하는 서브 4F2 구조의 디램 소자’입니다. 3.5F2 DRAM의 양산성을 고려하여 셀의 규격을 좀 더 구체적으로 설정하는 데 초점을 맞췄습니다. 해당 기술은 현재 미국에서도 특허 출원 중이며, 글로벌 반도체 시장에서 경쟁력을 확보할 핵심 기술 자산으로 활용될 전망입니다.

정혁제 나노팹기술개발센터 실장은 “기존 DRAM 공정과의 호환성을 유지하면서도 수직 구조를 효율적으로 배치하여 보다 미세화된 셀 소자를 구현한 것이 가장 큰 차별점”이라며 “향후 3D DRAM이나 HBM 메모리 응용에도 적합한 기반 기술로 작용할 것”이라고 말했습니다.

이어 그는 “이번 기술은 DRAM 고집적화 경쟁이 나노미터 공정 한계에 부딪힌 상황에서 새로운 방향성을 제시하는 사례가 될 것”이라고 덧붙였습니다.

또한 임채록 나노팹기술개발센터장은 “3.5F² DRAM의 셀 트랜지스터에 대한 HFSS 및 TCAD 시뮬레이션 결과, 전기적 특성이 우수함을 확인한 바 있다”며, “현재 해당 내용을 한국반도체학술대회, IEDM(International Electron Devices Meeting) 등 국내외 학회 발표와 함께, IEEE Transactions on Electron Devices 등 국제 저널 게재를 통해 기술적 우수성을 입증해 나가고 있다”고 말했습니다.

![[인더필드] ‘탄소중립 선봉장’ 풀무원 거점 음성 두부공장 가보니](https://www.inthenews.co.kr/data/cache/public/photos/20250940/art_17591045921966_86ea66_357x250.png)