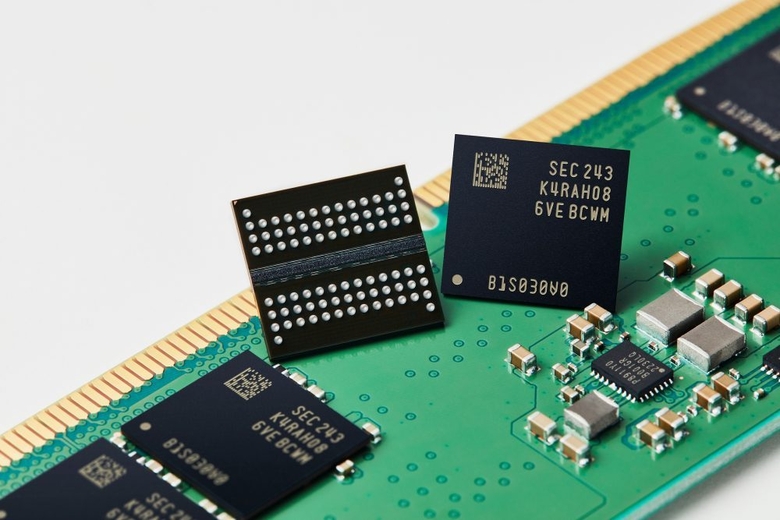

인더뉴스 권용희 기자ㅣ삼성전자[005930]는 12나노급 공정으로 16Gb(기가 비트) DDR5 D램 양산을 시작했다고 18일 밝혔습니다.

삼성전자는 "12나노급 D램은 이전 세대 제품 대비 생산성은 약 20% 향상됐고, 소비 전력은 약 23% 개선됐다"면서 "소비 전력 개선으로 데이터 센터 등을 운영하는 데 전력 운영 효율을 높일 수 있다"고 강조했습니다.

'12나노급 공정'은 트랜지스터 채널 길이가 12나노미터(㎚·10억분의 1m)라는 의미입니다. 삼성전자는 지난 2021년 10월 14나노 D램을 개발한 바 있습니다.

삼성전자는 유전율이 높은 신소재 적용으로 전하를 저장하는 커패시터의 용량을 늘렸습니다. 커패시터 용량이 커짐에 따라 데이터 구분이 명확해지고 오류 발생이 줄어든다고 설명했습니다.

동작 전류 기술과 데이터 구분 능력을 향상시키는 노이즈 저감 기술 등도 적용했습니다.

DDR5 규격의 12나노급 D램은 최고 동작 속도 7.2Gbps를 지원합니다. 이는 1초에 30GB 용량의 UHD영화 2편을 처리할 수 있는 속도입니다.

삼성전자는 지난해 12월 AMD 플랫폼 기반 호환성 검층을 마친 바 있습니다. 향후 12나노급 D램 라인업을 지속적으로 확대해 데이터센터·인공지능·차세대 컴퓨팅 등의 고객 수요에 맞춰 공급을 진행하겠다는 계획입니다.

이주영 삼성전자 메모리사업부 DRAM개발실장(부사장)은 “삼성전자는 대용량 처리가 요구되는 컴퓨팅 시장 수요에 맞춰 고성능, 고용량을 확보할 뿐만 아니라 높은 생산성으로 제품을 적기에 상용화하여 D램 시장을 지속 선도해 나갈 것”이라고 밝혔습니다.

차세대 컴퓨팅 시장 수요 맞춰 포트폴리오 다각화 나서

삼성전자는 12나노급 D램을 포함하여 차세대 컴퓨팅 시장 수요에 맞춘 제품 포트폴리오 확장에 나서고 있습니다.

지난 12일 삼성전자는 컴퓨트 익스프레스 링크(CXL) 2.0을 지원하는 128GB CXL D램을 개발했다고 밝혔습니다.

CXL는 CPU와 함께 고성능 서버 시스템을 효율적으로 활용하기 위한 인터페이스입니다. 메인 D램과 공존하면서 대역폭과 용량을 확장할 수 있어 인공지능, 머신러닝 등 차세대 컴퓨팅 시장에서 주목받고 있습니다.

CXL 2.0 D램은 고속 인터페이스 규격인 PCle 5.0을 지원하며, 최대 35GB/s의 대역폭을 제공합니다.

메모리 풀링 기능도 지원합니다. 서버 플랫폼에서 여러 개의 CXL 메모리를 묶고 여러 호스트가 필요한 만큼 메모리를 나누어 사용할 수 있는 기술입니다.

삼성전자는 "메모리 풀링 기술은 CXL 메모리의 전 용량을 유휴 영역 없이 사용 할 수 있게 돕는다"며 "효율적인 메모리 사용이 가능해 서버 운영비를 절감 할 수 있다"고 설명했습니다.

삼성전자는 지난해 5월 CXL 1.1 기반 CXL D램을 개발을 진행한 바 있습니다.

삼성전자 메모리사업부 신사업기획팀장 최장석 상무는 "삼성전자는 CXL 컨소시엄의 이사회 멤버로서 CXL 기술을 선도하고 있다"면서 "데이터센터/서버/칩셋 등 글로벌 기업들과의 협력으로 CXL 생태계를 더욱 확장해 나갈 것"이라고 말했습니다.